点击右上角![]() 微信好友

微信好友

朋友圈

朋友圈

请使用浏览器分享功能进行分享

2025年,全球EDA市场再度直面新的外部环境变化。产业格局的波动,让中国集成电路产业更加坚定走核心技术自主之路。

EDA是半导体产业不可或缺的核心基础工具链,承担着芯片开发过程中的核心工作。据统计,2024年全球芯片市场规模已超过6000亿美元,而数字芯片为该领域的核心分支,占整个芯片市场约60%的份额。受人工智能算力需求爆发驱动,数字芯片市场正进入高速增长周期,

因此,数字EDA和高端IP在产业中的地位至关重要。在此背景下,市场对国产EDA解决方案的需求持续升温。“国内唯一同时具备数字EDA工具、高端接口IP以及系统和封装工具的平台型公司”——上海合见工业软件集团有限公司(简称“合见工软”)跃入大众视野。

这是一支由全球EDA行业的优异人才组成的团队。2020年,他们放弃稳定高薪,投身高投入的EDA赛道,誓要为中国芯片设计打造自主的基础设施。

“中国庞大的电子设计与制造市场,以及完整的产业链,为孕育世界级的EDA公司提供了独一无二的土壤。”合见工软联合创始人、总经理徐昀说,“在这样的土壤中,合见工软的目标是超越。”

应时而生,“EDA梦之队”全球突围

EDA被誉为“芯片之母”,是集成电路产业最上游的设计工具,然而,该领域长期Synopsys、Cadence及Siemens EDA三巨头主导,它们占据全球约70%、中国80%的市场份额。其通过持续并购构筑完整工具链生态,形成显著技术壁垒。在新的全球产业格局变化下,中国必须在设计高端芯片所不可或缺的数字EDA工具这一核心环节实现自主。

合见工软的故事,始于中国集成电路对核心工具链自主化的迫切呼唤。徐昀表示,“我们是一家应运而生的公司。”它的诞生,承载着推动产业基础创新的时代使命。

因此,合见工软创始团队精准选择产业最急需、壁垒最高的领域——数字EDA作为主攻方向。

数字EDA专指用于设计CPU、GPU、AI芯片等大规模复杂数字芯片的软件工具链,负责将抽象算法和逻辑转化为芯片中数十亿晶体管的具体连接与布局,是技术最复杂、壁垒最高的核心环节。国内企业大多处于“点工具”替代阶段,难以形成可对标国际领先技术的能力。

使命所在,2020年5月,合见工软在上海成立,目标从这一核心环节实现系统性突破。

目前,合见工软员工已达1200人,规模居全国EDA公司前二,并位列全球前五。

堪称“EDA梦之队”的合见工软,甫一亮相就吸引了资本的密集关注。国家大基金、中国互联网投资基金等资本迅速入场,腾讯、上汽、国新基金、武岳峰科创等产业及国家级基金持续加持。至今,合见工软累计融资额已达45亿元。

顶尖的人才、时代的浪潮、雄厚的资本,三者合一,为合见工软的传奇拉开了序幕。

他们要做的,是从零开始,打造一个拥有完全自主知识产权、能够参与全球竞争的世界级EDA公司。

“我们从第一天起就要求,所有产品的研发要从零做起,架构必须自研创新。”徐昀强调,这种对知识产权的坚持,是他们走向全球市场的底气。

并购整合,以数字EDA为基石构建全栈能力

在中国高端芯片自主设计的道路上,芯片公司几乎都面临三大挑战:如何突破单芯片的算力极限?如何确保复杂设计一次成功?又如何将设计高效转化为可量产、高性能的产品?

围绕这些核心挑战,合见工软选择了一条“自研+并购”的整合式发展路径,在短短5年内推出近40款产品,以全流程数字EDA工具链为基石,向产业链上下游延伸,构建涵盖高性能IP与系统级EDA的完整解决方案。

创立初期,合见工软聚焦于解决“如何确保复杂设计一次成功”的验证难题。验证占芯片设计70%工作量,是最易出错、成本最高的环节。尤其对大芯片,一次流片失败可能导致数亿元损失。

因此,合见工软在2021年10月推出了国内首款自主知识产权的商用级数字仿真器,正式打破了国际EDA高端仿真工具的垄断,对EDA国产化意义重大。此产品面世后,经过了百万量级客户实战项目用例打磨淬炼和持续迭代优化,已在50+个关键芯片项目中成功应用,得到了国内头部客户的认可。

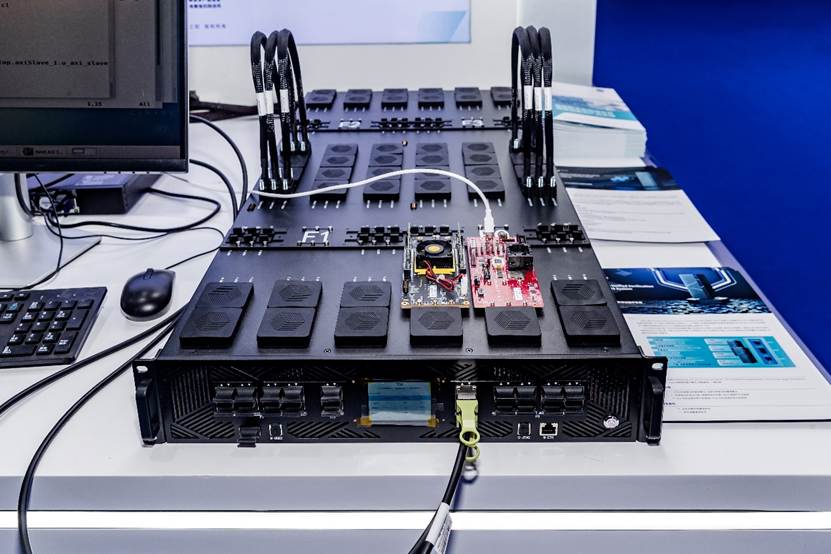

同样在2021年,合见工软推出性能比肩国际水平的全场景硬件验证系统,大幅缩短仿真验证周期,帮助客户提升流片成功率,赢得首批头部客户信赖。

图注:合见工软硬件验证平台

在筑牢验证根基后,合见工软瞄准复杂高端芯片的另一关键支柱“接口IP”技术,这是构建高性能计算和人工智能芯片的重要组成部分。

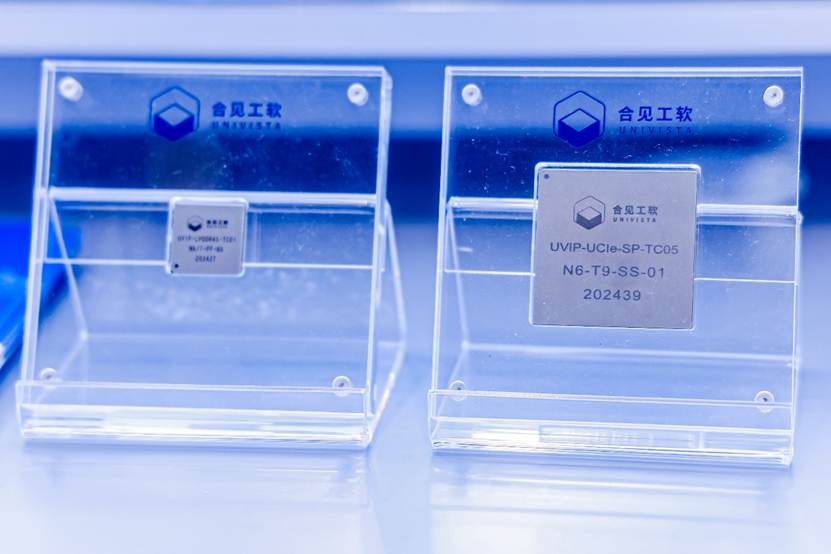

几年来合见工软推出了全面的国产接口IP矩阵,智算组网类IP方案和针对先进封装芯粒(Chiplet)集成的标准IP方案系列产品,均支持多家先进工艺,已经流片验证,现已在国内领先IC企业芯片中成功部署,引领智算、HPC、通信、自动驾驶、工业物联网等领域大算力芯片的性能突破及爆发式发展。

图注:合见工软IP产品测试芯片

最后,围绕“如何将设计高效转化为一站式方案”的实现挑战。合见工软整合形成闭环解决方案。客户可将高性能IP与其硬件验证平台结合,在设计-验证-封测整个流程解决设计中的挑战,提前验证多芯粒系统与智算集群组网,降低架构创新风险。

该产品矩阵贯穿芯片从架构设计到物理实现的完整流程。在后端,其可测性设计与良率分析工具助力提升量产良率;在系统集成端,其先进封装与高速PCB设计平台确保从芯片到板卡的可靠实现。

通过关键并购与整合,合见工软为攻克上述挑战提供了国产化工具链支撑,成为“国内唯一同时具备数字EDA工具、接口IP以及系统与封装工具的公司”。

目前,合见工软服务客户和合作已覆盖超三百家芯片设计企业、科研机构与高校,国内头部算力芯片设计公司多数已进入其客户名单。

徐昀指出,“我们能针对国内独特的产业环境提供真正差异化的方案,并且能够及时响应客户定制化需求。”

2025年6月,合见工软发布了下一代EDA战略,将数字验证最核心的基础工具,及支持大规模芯片设计的高端硬件验证平台,均实现了架构级迭代创新,成为国产EDA技术创新的重大进展,多项性能比肩国际标杆水平,目标打破数字高端大芯片验证EDA的国际厂商垄断。

创新加速,成为全球领先EDA公司

在实现稳步发展后,合见工软着眼于塑造国产EDA新格局。

“国内EDA产业长期‘小而散’,多数企业只能提供点工具,形不成合力。”徐昀指出:“中国需要诞生属于自己的世界级EDA平台公司。”为此,合见工软表示,未来将继续推动产业整合,构建完整、协同的国产工具链体系。

基于领先的技术与整合而成的平台能力,合见工软的视野同步迈向全球。公司已在新加坡、日本设立分支机构,其自主研发的高速接口IP与验证解决方案正逐步接受国际市场的检验。

在生态建设上,合见工软对内构筑“人才护城河”,对外积极开放协同。公司与清华、北大等高校共建实验室,将前沿EDA工具引入教学,培养下一代芯片设计与EDA复合型人才。同时,合见工软协同产业伙伴推动数据库、国产芯粒互联标准等底层规范建立,以降低协作成本,提升生态效率。

展望未来,合见工软目标清晰。徐昀透露,作为中国芯片自主创新的“底座型”伙伴,公司将持续服务好国内高端芯片客户,提供全流程解决方案;继而,公司将凭借技术优势,有步骤地参与全球市场竞争,为世界带来中国的EDA领先选择。